“I don’t make mistakes. I make prophecies which immediately turn out to be wrong.”

简介

本文将对香山的分支预测顶层模块BPU进行介绍,BPU为取值目标队列(FTQ)提供预测的取址目标,BPU主要包含如下逻辑:

- 覆盖预测逻辑(后级预测对前级进行覆盖)

- 流水线握手(各级之间以及BPU和FTQ之间)

- 全局分支历史管理

基本结构及参数

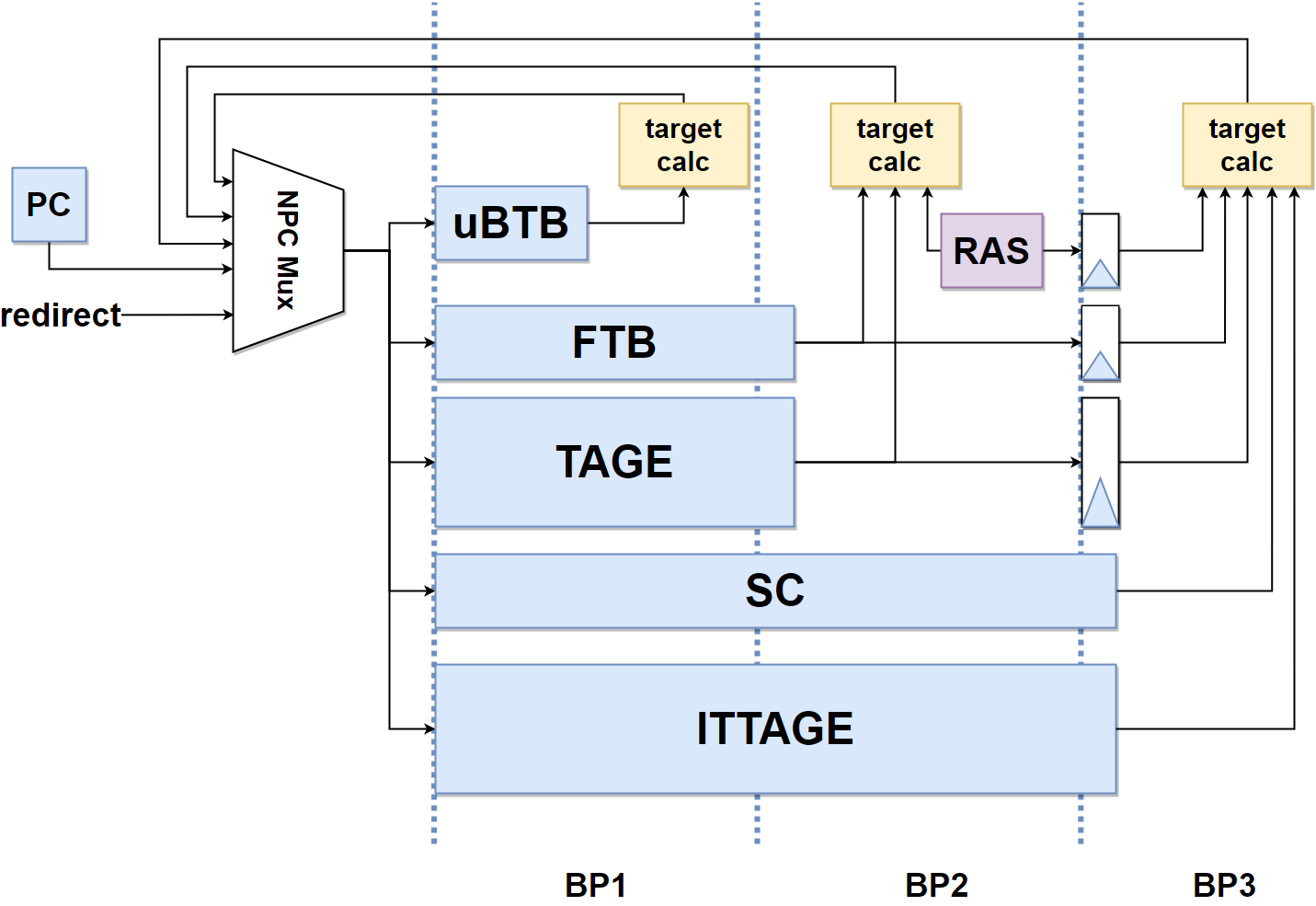

分支预测单元采用多级混合预测架构,主要包含两个部分

Next Line Predictor (NLP):$\mu $BTB

Accurate Predictor (APD): FTB/TAGE-SC/ITTAGE/RAS

Input/Output

BasePredictor

IO.in

预测器的基本输入如下:

1 | class BasePredictorInput (implicit p: Parameters) extends XSBundle with HasBPUConst { |

IO.out

1 | class BasePredictorOutput (implicit p: Parameters) extends XSBundle with HasBPUConst { |

IO

1 | class BasePredictorIO (implicit p: Parameters) extends XSBundle with HasBPUConst { |

PredictorIO

1 | class PredictorIO(implicit p: Parameters) extends XSBundle { |

预测器逻辑

握手逻辑

BPU 的各个流水级都会连接 FTQ,一旦第一个预测流水级存在有效预测结果,或者后续预测流水级产生不同的预测结果,和 FTQ 的握手信号有效位都会置高。

1 | // 握手逻辑 |

重定向

当不同预测阶段的预测结果不一致时,需要进行重定向:

1 | val s3_redirect_on_br_taken = resp.s3.full_pred.real_br_taken_mask().asUInt =/= previous_s2_pred.full_pred.real_br_taken_mask().asUInt |

流水线逻辑

不同的预测stage之间依靠寄存器保存中间结果,当某一级发射后,相应的PC值以及分支历史等信息进入下一级:

1 | val reset_vector = DelayN(io.reset_vector, 5) |

当发生重定向时,需要进行流水线冲刷

1 | // 流水线冲刷 |

分支历史管理

1 | // History manage |

结果保存

每个stage产生的结果保存在对应的Priority Mux中

1 | val npcGen = new PhyPriorityMuxGenerator[UInt] |

reset

1 | when (RegNext(RegNext(reset.asBool) && !reset.asBool)) { // reset release |