本文将对使用modelsim进行verilog电路仿真及测试的过程进行概述

工程建立及模块编写

此处较为简单,请参考网上关于Modelsim的使用说明,我们以一个简单的异步复位同步释放寄存器为例,其代码如下:

1 | module Register (q, clk, rst, d); |

TestBench

完成模块编写后,我们需要针对该模块编写对应的测试用例,在测试用例中,我们要创建对应的模块,给定输入信号作为激励,观察输出是否与预期一致,测试模型如下,其中DUT即为我们的待测单元:

1 |

|

仿真

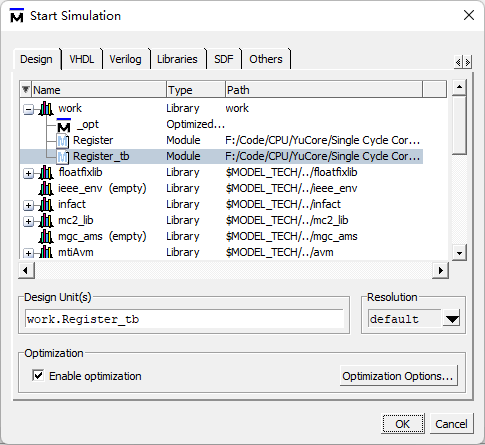

在完成testbench的编写后,我们可以对其进行仿真,点击Compile All编译所有的组件,然后点击Simulate - Start Simulation,在work中选择待仿真的对象,此处不要勾选Enable Optimization,否则会出现无法导入信号的情况

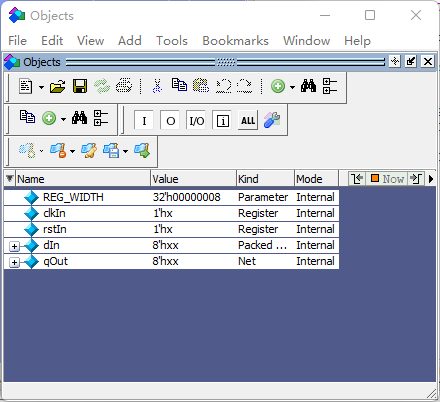

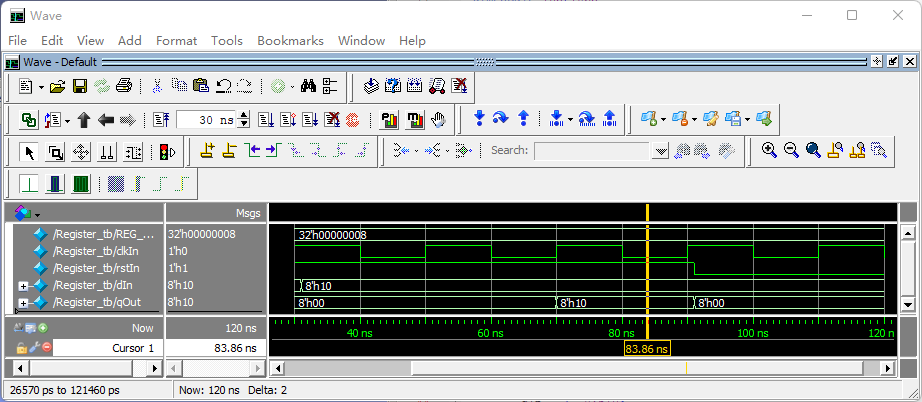

在objects中选择待观测的信号,右键选择Add Wave,即可将信号导入波形图中: