虚拟体验也好,梦也罢,这个世上的信息,既现实也虚幻;无论如何,人一生所能接触的事物也只是沧海一粟罢了

CPU组成部分

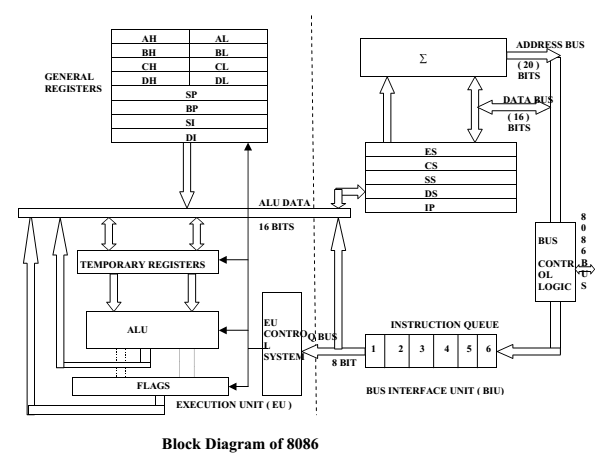

CPU由控制器和运算器两个部分组成。其逻辑结构图如下所示:

上面的图中,左半部分为指令执行单元(EU),右半部分为总线接口单元(BIU),下面针对这两个单元分别介绍:

总线接口单元BIU

功能

作为CPU与外部(存储器和IO)的接口,提供16位双向数据线和20位地址线,完成所有外部总线操作,包括地址形成、取指令、指令排队、读写操作数和总线控制。

组成

- 16位段寄存器:CS/DS/ES/SS

- 16位指令指针寄存器IP

- 20位物理地址加法器(图中的$\sum$):将16位逻辑地址变为20位物理地址

- 六字节指令队列:存放6字节指令代码

- 总线控制逻辑电路:发出总线控制信号

工作过程

- CS+IP进行20位寻址,送往地址总线,总线控制逻辑发出存储器读信号$\overline{\textrm{RD}}$,按给定地址从存储器中取出指令,送到指令队列中。

- 指令队列可以存储六字节指令,当指令队列空余时,BIU自动取指令;指令队列已满并且EU未申请读写存储器操作时,BIU空闲。

- EU从指令队列取走指令,经过译码后向BIU申请从存储器或IO端口读写操作。只要收到EU送来的逻辑地址,BIU将通过地址加法器转换成物理地址,在读写周期访问存储器或IO完成IO操作。(EU执行指令,BIU传输运算结果)

- BIU控制指令指针寄存器IP自动指向下一条待执行指令,并从后续地址存放的指令序列中取指令填充指令队列

指令执行部件EU

功能

完成译码和执行指令的功能

组成

- 算术逻辑单元ALU:完成8位或16位二进制运算

- 标志寄存器:保存ALU运算结果特征

- 寄存器组:4个通用16位寄存器(AX为累加器),4个专用16位寄存器

- EU控制器:从指令队列取指令、指令译码和时序控制部件

工作过程

- EU从指令队列取指令并译码,如果指令需要访问存储器或IO,则EU通过内部16位总线将逻辑地址送给BIU,BIU访问存储器或IO,获得操作数发送给EU,EU执行指令

- ALU完成各种算数及逻辑运算,运算操作数可以从存储器或寄存器组取得,运算结果由内部总线送至寄存器组或BIU的内部寄存器。运算后结果的特征改变标志寄存器flags的某些状态位,可供测试或判断及转移指令之用。

- 一般情况下EU从指令队列而非存储器中取指令,所以取指令和执行可以并行操作。但如果有转移、调用或返回指令,会导致指令队列失效,这时必须新取得指令后才可以继续执行,但是这种情况比较少见,所以EU和BIU相互配合的非同步并行提高了效率。

CPU工作过程

一般来说,CPU的工作过程可以概括为:

1 | for(;;){ |

CPU的工作状态

CPU可以分为管态(特权态)与目态(常态)

8086CPU介绍

本文以经典的x86系列CPU的鼻祖8086CPU为例,详细介绍一下CPU的系统结构

CPU引脚及其功能

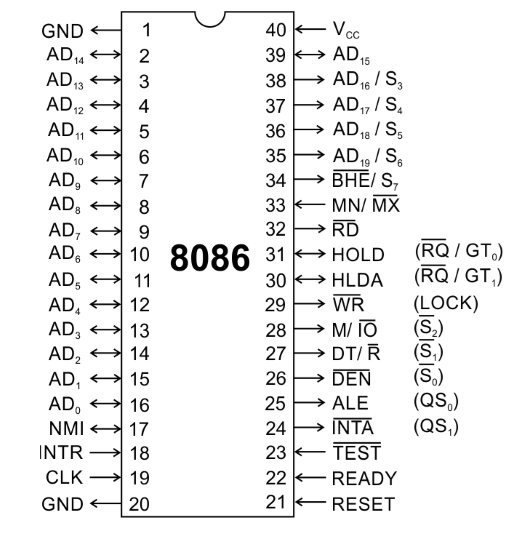

8086CPU的外部引脚图如下所示:

地址线

地址线为AD0-AD19共20条,其中AD0-AD15为16条地址/数据总线,而AD16-AD19为地址/数据/状态三态输出、分时复用。

数据线

数据线为AD0-AD15共16条