If I can only remember one thing, I will remember your name

寄存器就是CPU中的一些时序逻辑电路,属于暂时存放参与运算的数据和结果。速度非常快,容量非常小。

常用寄存器(ARM)

通用寄存器组

异常综合表征寄存器ESR_ELn

ESR寄存器用于异常处理程序确定异常原因。

常用寄存器(x86,了解即可)

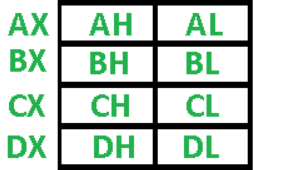

通用寄存器组

功能

位于EU中,可以存放16位数据或地址,也可以分为8个8位寄存器使用(只能放数据)

- AX:累加器

- BX:基址寄存器

- CX:计数寄存器

- DX:数据寄存器

通用寄存器会有一些特殊用途。

指针和变址寄存器

下面这些寄存器都是指向内存的

- BP:基址寄存器,与SP共同组成操作数地址(栈底地址)

其内部存放指向系统栈栈底的指针,调用子程序时第一句都是push EBP,就是为了保存栈基址,因为ESP总是会变化的

1 | => 0x7cda: push %ebp # 保存栈基址 |

- SP:堆栈指针寄存器,其内部存放指向系统栈栈顶的指针,PUSH时减小(栈向下生长),在x86中,esp总是4的倍数

- SI:源操作数偏移量

- DI:目的操作数偏移量,在很多字符串操作指令中,DS:ESI指向源串,ES:EDI指向目标串

段寄存器

段寄存器给出了当前段的基地址,配合IP指令寄存器,可以实现基址+偏移地址的寻址过程。在8086中,CPU可以寻址20位,但寄存器只有16位,因此需要分段。段寄存器给出相应逻辑段首地址。

代码段寄存器CS

数据段寄存器DS

堆栈段寄存器SS

堆栈段寄存器和堆栈段指针寄存器SP共同构成了堆栈段的地址[SS:SP]

附加段寄存器ES

段寄存器寻址过程(实模式下)

假设我们有一条地址,其表示为[CS:IP],而计算机的位数为16位,那么这条指令的实际物理地址计算为:

例如有一个指令执行的地址为[f000:fff0],那么其实际物理地址为:

指令指针寄存器EIP

8086设置了一个16位指令指针寄存器IP,用于存放下一条指令的偏移地址,从而控制指令序列执行流程。由BIU自动修改,在每条指令执行后递增。可以通过CALL、RET、JMP以及conditional jump等命令进行修改。IP也是指向内存的。

标志寄存器flags

一共有6个状态标志和3个控制标志,用于控制conditional jump(JP,JN,J[N]Z,J[N]C,J[N]O等)

状态标志

- CF:有进位或借位为1

- PF:奇偶校验,低8位有偶数个1时PF为1

- AF:辅助进位标志,低4位向高四位进位或借位时,AF=1

- ZF:运算结果为0时ZF=1

- SF:符号标志位,最高位为1时SF=1

- OF:溢出标志位,产生溢出为1

控制标志

- TF:单步标志,可设置单步执行,每执行一次指令,触发一个中断

- IF:中断标志位,IF=1允许CPU响应可执行中断

- DF:方向标志位,在串操作指令中,DF=0由低地址向高地址进行操作。

内存管理寄存器

x86提供了四个内存管理计算器,分别为GDTR、LDTR、IDTR和TR,用于指定内存分段管理所用系统表的基地址

全局描述表寄存器GDTR

GDTR寄存器用于存放全局描述表GDT的32位线性基地址和16位表限长值,基地址指明表中字节0在线性地址空间中的地址,而表长度指明GDT表的字节长度值。由于机器刚上电或复位后基地址默认为0,而长度被设置为0xFFFF,所以在保护模式初始化过程中必须给GDTR一个新值。

控制类寄存器

共有5个控制类寄存器CR0-CR4,可以控制CPU的特性

CR01

功能

CR0寄存器的主要功能是实现对于CPU的控制,其中比较重要的是实现实模式到保护模式的切换

描述

CR0长度为32-bit,具体位描述如下:

| Bit | Name | Full Name | Description |

|---|---|---|---|

| 0 | PE | Protected Mode Enable(保护模式和实模式切换) | If 1, system is in protected mode, else system is in real mode |

| 1 | MP | Monitor co-processor | Controls interaction of WAIT/FWAIT instructions with TS flag in CR0 |

| 2 | EM | Emulation | If set, no x87 floating-point unit present, if clear, x87 FPU present |

| 3 | TS | Task switched | Allows saving x87 task context upon a task switch only after x87 instruction used |

| 4 | ET | Extension type | On the 386, it allowed to specify whether the external math coprocessor was an 80287 or 80387 |

| 5 | NE | Numeric error | Enable internal x87 floating point error reporting when set, else enables PC style x87 error detection |

| 16 | WP | Write protect | When set, the CPU can’t write to read-only pages when privilege level is 0 |

| 18 | AM | Alignment mask | Alignment check enabled if AM set, AC flag (in EFLAGS register) set, and privilege level is 3 |

| 29 | NW | Not-write through | Globally enables/disable write-through caching |

| 30 | CD | Cache disable | Globally enables/disable the memory cache |

| 31 | PG | Paging | If 1, enable paging and use the § CR3 register, else disable paging. |

CR3

CR3寄存器是比较重要的一个寄存器,用于线性地址到物理地址的转换过程中,CR3保存了页目录的基地址(物理地址),当进程发生切换时,必须更换至相应进程的页目录。同理,内核作为一个进程,也有自己的页目录。